# Lecture 8 - Three-port S-Parameter design techniques

Microwave Active Circuit Analysis and Design

Clive Poole and Izzat Darwazeh

Academic Press Inc.

Slide1 of 46

# **Intended Learning Outcomes**

#### Knowledge

- Understand the use of three-port representation for microwave transistors in the design of feedback circuits.

- Understand the power of feedback mappings in circuit design, the different classifications and how to apply them.

- Understand and be able to interpret reverse feedback mappings.

- Skills

- Be able to calculate the shunt and series feedback three-port S-parameters from measured two-port S-parameters.

- Be able to calculate two-port S-parameters for common base/gate and common collector/drain configurations, given the common emitter/source two-port S-parameters for a device (configuration conversion).

- Be able to calculate the two-port S-parameters of a transistor with arbitrary shunt and series feedback.

- Be able to construct and interpret feedback mappings and reverse feedback mappings.

- Be able to determine the optimum reactive feedback termination required to generate negative resistance in a given transistor.

## **Table of Contents**

Three-port immittance parameters

Three-port S-parameters

Configuration conversion

Feedback mappings

Application of three-port design techniques

Reverse feedback mappings

イロト イポト イヨト イヨト

#### **Three-port immittance parameters**

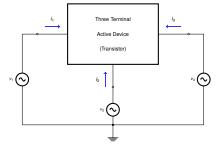

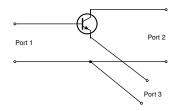

Let us begin with an immittance parameter approach, by considering a transistor as being a floating three-port with all three terminals independently referenced to ground, as shown in figure 1. We can characterise the device in terms of a three-port Y-matrix, referred to as the Indefinite Admittance Matrix or 'IAM'[3] and defined as:

$$\begin{bmatrix} i_{1} \\ i_{2} \\ i_{3} \end{bmatrix} = \begin{bmatrix} Y_{11} & Y_{12} & Y_{13} \\ Y_{21} & Y_{22} & Y_{23} \\ Y_{31} & Y_{32} & Y_{33} \end{bmatrix} \begin{bmatrix} v_{1} \\ v_{2} \\ v_{3} \end{bmatrix}$$

(1)

Figure 1 : Indefinite admittance matrix definition

## **Table of Contents**

Three-port immittance parameters

Three-port S-parameters

Configuration conversion

Feedback mappings

Application of three-port design techniques

Reverse feedback mappings

イロト イポト イヨト イヨト

#### **Three-port** S-parameters

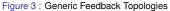

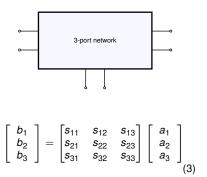

For the three-port network of figure 2 we can write:

$$b_{1} = s_{11}a_{1} + s_{12}a_{2} + s_{13}a_{3} b_{2} = s_{21}a_{1} + s_{22}a_{2} + s_{23}a_{3} b_{3} = s_{31}a_{1} + s_{32}a_{2} + s_{33}a_{3}$$

$$(2)$$

Where  $a_i$  and  $b_i$  are the scattering power wave variables.

Note: upper case  $S_{ij}$  is used to represent the *S*-parameters of a two-port. Lower case  $s_{ij}$  will be used to represent the *S*-parameters of networks with three or more ports.

Figure 2 : Three-port network with power waves

# **Feedback Topologies**

æ

・ロト ・聞 ト ・ ヨ ト ・ ヨ ト ・

# **3-port S-parameters**

- Feedback design requires that the active device is represented as a 3-port network, characterised by a set of 3-port S-parameters

- The 3-port S-parameters can be directly measured using special test jigs, or, more commonly calculated from the measured 2-port S-parameters

- By convention, port 3 is the port to which the feedback termination will be applied.

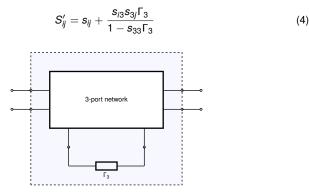

#### **3-port with feedback**

- The two-port comprised of a three port plus feedback termination attached to port 3 is referred to as the reduced two-port.

- The two-port S-parameters of the reduced two-port in figure ?? can be expressed in terms of the three-port S-parameters, s<sub>ij</sub>, and a third port termination, Γ<sub>3</sub>, as follows[2]:

#### **Classification of three-port S-parameters**

Slide10 of 46

э

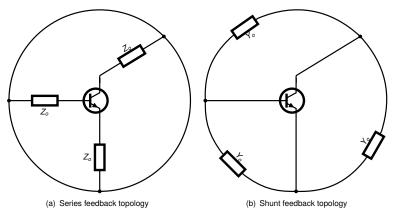

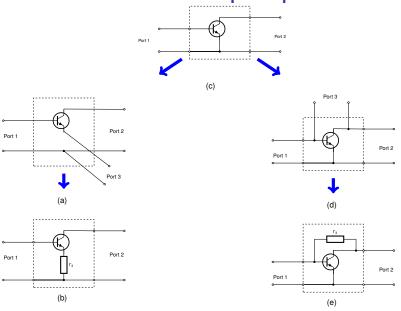

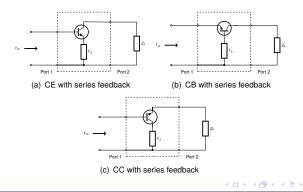

### Series feedback three-port S-parameters

Consider the case of the series feedback three-port shown in figure 4(a) (previous slide). The three-port *S*-matrix for this network can be written as:

$$\begin{bmatrix} b_1 \\ b_2 \\ b_3 \end{bmatrix} = \begin{bmatrix} s_{11} & s_{12} & s_{13} \\ s_{21} & s_{22} & s_{23} \\ s_{31} & s_{32} & s_{33} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \\ a_3 \end{bmatrix}$$

(5)

Bodway showed that the sum of any row or column of this matrix is unity, i.e.[2]:

$$\sum_{j=1}^{3} s_{ij} = \sum_{i=1}^{3} s_{ij} = 1$$

(6)

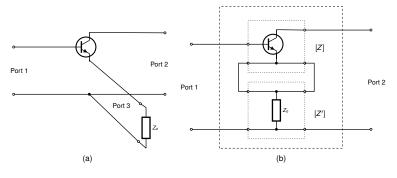

#### Series feedback three-port S-parameter derivation

Figure 5 shows the two-port of figure 4(b) redrawn in order to illustrate the fact that this two-port can be considered as the measured common source transistor two-port connected in series with a passive two-port, comprising a shunt matched termination  $Z_o$  (i.e.  $\Gamma_3 = 0$ ).

Figure 5 : Series feedback circuit analysis

Slide12 of 46

#### Series feedback three-port S-parameter derivation

The transistor in figure 5(b) can be represented by its normalised two-port impedance matrix. If we are starting with measured two-port *S*-parameters then we need to convert them to *z*-parameters.

$$[z] = \begin{bmatrix} z_{11} & z_{12} \\ z_{21} & z_{22} \end{bmatrix}$$

(7)

The normalised impedance matrix of the lower two-port in figure 5(b), consisting of a shunt matched termination,  $Z_o$ , is given by:

$$\begin{bmatrix} z' \end{bmatrix} = \begin{bmatrix} 1 & 1 \\ 1 & 1 \end{bmatrix}$$

(8)

Since these two two-port networks are in series, the overall normalised impedance matrix is the sum of the two *z*-matrices in (7) and (8), i.e.:

$$[z_{T}] = \begin{bmatrix} (z_{11}+1) & (z_{12}+1) \\ (z_{21}+1) & (z_{22}+1) \end{bmatrix}$$

(9)

#### Series feedback three-port S-parameter derivation

The *S*-matrix of the complete two-port of figure 5 can then be found by transformation of equation (9) back into the *S*-domain, and the remaining five three-port *S*-parameters can be found by application of Bodway's relationship (6):

$$\begin{array}{c} s_{13} = 1 - s_{11} - s_{12} \\ s_{31} = 1 - s_{11} - s_{21} \\ s_{23} = 1 - s_{21} - s_{22} \\ s_{32} = 1 - s_{12} - s_{22} \\ s_{33} = 1 - s_{31} - s_{32} \end{array} \right\}$$

(10)

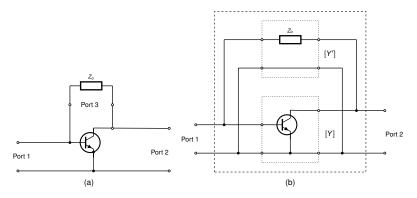

#### Shunt feedback three-port S-parameter derivation

The shunt feedback three-port shown in figure 6(a) does not have the same three-port *S*-matrix as in the series feedback case of figure 5(a), so Bodway's relationship (6) does not apply in this case.

Figure 6 : Shunt feedback circuit analysis

Slide15 of 46

#### Shunt feedback three-port S-parameter derivation

The two-port of figure 6(b) can be considered as a passive two-port, comprising a series matched admittance,  $Y_o = 1/Z_o$ , in parallel with the common emitter transistor, measured as a two-port. The transistor can be represented by its normalised common source admittance matrix by employing the transformations in Appendix **??**, namely:

$$[y] = \begin{bmatrix} y_{11} & y_{12} \\ y_{21} & y_{22} \end{bmatrix}$$

(11)

The normalised admittance matrix of the upper two-port in figure 6(b), consisting of a shunt matched termination is given by:

$$\begin{bmatrix} y' \end{bmatrix} = \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix}$$

(12)

イロト イポト イヨト イヨト

Since these two two-port networks are in parallel, the overall normalised admittance matrix is given by the sum of the two *y*-matrices in equations (11) and (12), as follows:

$$[y_{7}] = \begin{bmatrix} (y_{11}+1) & (y_{12}-1) \\ (y_{21}-1) & (y_{22}+1) \end{bmatrix}$$

(13)

The *S*-matrix for the two-port of figure 6(b) can then be found by converting (13) back into the *S*-domain. The remaining five three-port *S*-parameters can be found by application of the equations (14).

#### Shunt feedback three-port S-parameter derivation

In the shunt feedback case the sum of each row or column of the shunt three-port S-matrix no longer equals unity, but Bodway has provided the following relationships between the three-port S-parameters for the shunt feedback case:

$$\begin{array}{c} s_{13} = 1 + s_{11} - s_{12} \\ s_{31} = 1 - s_{21} + s_{11} \\ s_{23} = s_{21} - s_{22} - 1 \\ s_{32} = s_{12} - s_{22} - 1 \\ s_{33} = s_{31} - s_{32} - 1 \end{array} \right\}$$

(14)

As in the series feedback case, if any four of the three-port *S*-parameters are known then the remaining five can be determined from the relationships (14) above. The measurement of the two-port in figure 6(b) would therefore be sufficient to fully characterise the three-port.

#### Series feedback three-port S-parameters: Alternate derivation

In the case of series feedback, we could alternatively make use of the following definition of the series three-port S-parameter,  $s_{33}$ [5]:

$$s_{33} = \frac{\xi}{4-\xi} \tag{15}$$

Where  $\xi$  is the sum of the two-port *S*-parameters[4], i.e.:

$$\xi = S_{11} + S_{12} + S_{21} + S_{22} \tag{16}$$

Using the relationship in (15) we can now write the complete series three-port *S*-matrix, explicitly in terms of the original common emitter two-port *S*-matrix as follows :

$$\begin{bmatrix} s_{11} & s_{12} & s_{13} \\ s_{21} & s_{22} & s_{23} \\ s_{31} & s_{32} & s_{33} \end{bmatrix} = \begin{bmatrix} \left( S_{11} + \frac{\Delta_{11}\Delta_{12}}{4-\xi} \right) & \left( S_{12} + \frac{\Delta_{11}\Delta_{21}}{4-\xi} \right) & \frac{2\Delta_{11}}{4-\xi} \\ \left( S_{21} + \frac{\Delta_{22}\Delta_{12}}{4-\xi} \right) & \left( S_{22} + \frac{\Delta_{22}\Delta_{21}}{4-\xi} \right) & \frac{2\Delta_{22}}{4-\xi} \\ \frac{2\Delta_{12}}{4-\xi} & \frac{2\Delta_{21}}{4-\xi} & \frac{\xi}{4-\xi} \end{bmatrix}$$

(17)

Where :

$\Delta_{11} = 1 - S_{11} - S_{12} \qquad \qquad \Delta_{21} = 1 - S_{12} - S_{22} \\ \Delta_{12} = 1 - S_{11} - S_{21} \qquad \qquad \Delta_{22} = 1 - S_{21} - S_{22}$

◆□▶ ◆□▶ ◆□▶ ◆□▶ ● ○ ○ ○

#### Calculation of reduced two-port S-parameters

The two-port formed from a three-port device (e.g. transistor) plus feedback combination is referred to as a *reduced two-port*[2].

The feedback termination can be thought of as providing an extra degree of freedom to the standard design procedure since feedback allows a wide range of two-port S-parameters to be realised.

The two-port *S*-parameters of the reduced two-port can be expressed in terms of the three-port *S*-parameters,  $s_{ij}$ , and a third port termination,  $\Gamma_3$ , as follows[2]:

$$S'_{ij} = s_{ij} + \frac{s_{i3}s_{3j}\Gamma_3}{1 - s_{33}\Gamma_3}$$

(18)

Or in matrix form as :

$$\begin{bmatrix} S_{11}' & S_{12}' \\ S_{21}' & S_{22}' \end{bmatrix} = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix} + \frac{\Gamma_3}{1 - s_{33}\Gamma_3} \begin{bmatrix} s_{13}s_{31} & s_{13}s_{32} \\ s_{23}s_{31} & s_{23}s_{32} \end{bmatrix}$$

(19)

#### Calculation of reduced two-port S-parameters

In the special case where port three of the series feedback three-port in figure 5(a) is terminated with a short circuit (i.e.  $\Gamma_3 = 1 \angle 180^\circ$ ), this reduces to :

$$\begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} = \begin{bmatrix} \left( s_{11} - \frac{s_{13}s_{31}}{1 + s_{33}} \right) & \left( s_{12} - \frac{s_{13}s_{32}}{1 + s_{33}} \right) \\ \left( s_{21} - \frac{s_{23}s_{31}}{1 + s_{33}} \right) & \left( s_{22} - \frac{s_{23}s_{32}}{1 + s_{33}} \right) \end{bmatrix}$$

(20)

Similarly, when port three of the shunt feedback three-port in figure 6(a) is terminated with an open circuit (i.e.  $\Gamma_3 = 1 \angle 0^{\circ}$ ) equation (19), reduces to:

$$\begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} = \begin{bmatrix} \left( s_{11} + \frac{s_{13}s_{31}}{1 - s_{33}} \right) & \left( s_{12} + \frac{s_{13}s_{32}}{1 - s_{33}} \right) \\ \left( s_{21} + \frac{s_{23}s_{31}}{1 - s_{33}} \right) & \left( s_{22} + \frac{s_{23}s_{32}}{1 - s_{33}} \right) \end{bmatrix}$$

(21)

Equations (20) and (21) simply express the original two-port *S*-matrix (which is Common Emitter/Common Source by default) in terms of the series and shunt feedback three-port *S*-parameters, respectively.

<u>Note</u>: the three-port *S*-parameters for the series and shunt feedback three-ports are different.

イロト 不得 とくほ とくほ とう

## **Table of Contents**

Three-port immittance parameters

Three-port S-parameters

#### Configuration conversion

Feedback mappings

Application of three-port design techniques

Reverse feedback mappings

イロト イポト イヨト イヨト

# **Configuration conversion**

Figure 7 : Series CE three-port definitions for a transistor

- ► The two-port *S*-parameters of any transistor configuration may be determined by starting with the series feedback three-port of 7 then simply rearranging the three-port *S*-matrix and adding a short circuit ( $\Gamma_3 = 1 \angle 180^\circ$ ) to the appropriate port.

- Depending on the type of device used (BJT or FET), the remaining two-ports represent either Common Emitter/Source (ces), Common base/gate (cbg) or Common collector/drain (ccd) configuration depending on which port has been shorted.

- This provides a simple means of determining the two-port S-parameters for the three possible transistor configurations from one set of measurements, without having to measure a different set of S-parameters for each configuration.

# **Configuration conversion**

Consider the BJT shown in figure 7, which is characterised as a series feedback three-port network with the following *S*-matrix:

$$\begin{bmatrix} b_1 \\ b_2 \\ b_3 \end{bmatrix} = \begin{bmatrix} s_{11} & s_{12} & s_{13} \\ s_{21} & s_{22} & s_{23} \\ s_{31} & s_{32} & s_{33} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \\ a_3 \end{bmatrix}$$

(22)

We can 'reduce' the three-port of figure 7 to one of the three possible *reduced two-port* configurations by connecting one of the ports to ground, as follows:

- 1. Grounding port 1 gives the common base/gate reduced two-port.

- 2. Grounding port 2 gives the common collector/drain reduced two-port.

- 3. Grounding port 3 gives the common emitter/source reduced two-port.

In signal terms, 'grounding' means applying a short circuit termination ( $\Gamma=1\angle180^o)$  to the port in question.

By convention, two-port *S*-parameters are usually measured in the common emitter/source configuration, and manufacturers only supply *S*-parameter data in this configuration. In the following sections, we will derive some useful conversion formulae that allow the reduced two-port *S*-parameters for the other two configurations to be calculated given the three-port *S*-parameters of the circuit in figure 7.

イロト 不得 とくほ とくほ とう

#### **Common base/gate configuration**

To convert from Common Emitter/Source configuration to Common base/gate (*cbg*) we swap ports 1 and 3 of figure 4(a). In terms of the original common emitter/source three-port *S*-parameters the three-port *S*-matrix for the *cbg* configuration then becomes:

$$\begin{bmatrix} s^{cbg} \end{bmatrix} = \begin{bmatrix} s_{33} & s_{32} & s_{31} \\ s_{23} & s_{22} & s_{21} \\ s_{13} & s_{12} & s_{11} \end{bmatrix}$$

(23)

Applying a short circuit at the new port three (the base/gate terminal) results in the reduced two-port S-matrix of Common base/gate (*cbg*) configuration. In terms of the *ces* three-port S-parameters this can be written as follows:

$$\begin{bmatrix} S_{11}^{cbg} & S_{12}^{cbg} \\ S_{21}^{cbg} & S_{22}^{cbg} \end{bmatrix} = \begin{bmatrix} \left( s_{33} - \frac{s_{31}s_{13}}{1+s_{11}} \right) & \left( s_{32} - \frac{s_{31}s_{12}}{1+s_{11}} \right) \\ \left( s_{23} - \frac{s_{21}s_{13}}{1+s_{11}} \right) & \left( s_{22} - \frac{s_{21}s_{12}}{1+s_{11}} \right) \end{bmatrix}$$

(24)

### **Common collector/drain configuration**

To convert from Common Emitter/Source configuration to Common collector/drain (*ccd*) we swap ports 2 and 3 of figure 4(a). In terms of the original common emitter/source three-port *S*-parameters, the three-port *S*-matrix for the *ccd* configuration then becomes :

$$\begin{bmatrix} s^{ccd} \end{bmatrix} = \begin{bmatrix} s_{11} & s_{13} & s_{12} \\ s_{31} & s_{33} & s_{32} \\ s_{21} & s_{23} & s_{22} \end{bmatrix}$$

(25)

Applying a short circuit at the new port three (the collector/drain terminal) results in the reduced two-port *S*-matrix of Common collector/drain (*ccd*) configuration. In terms of the *ces* three-port *S*-parameters this can be written as follows:

$$\begin{bmatrix} S_{11}^{ccd} & S_{12}^{ccd} \\ S_{21}^{ccd} & S_{22}^{ccd} \end{bmatrix} = \begin{bmatrix} \left( s_{11} - \frac{s_{12}s_{21}}{1 + s_{22}} \right) & \left( s_{13} - \frac{s_{12}s_{23}}{1 + s_{22}} \right) \\ \left( s_{31} - \frac{s_{32}s_{21}}{1 + s_{22}} \right) & \left( s_{33} - \frac{s_{32}s_{23}}{1 + s_{22}} \right) \end{bmatrix}$$

(26)

Equations (24) and (26) allow the direct calculation of the two-port S-parameters for a transistor in common base/gate configuration or common collector/drain configuration, respectively, given the common emitter three-port S-parameters of the device.

## **Table of Contents**

Three-port immittance parameters

Three-port S-parameters

Configuration conversion

Feedback mappings

Application of three-port design techniques

Reverse feedback mappings

(4 個) トイヨト イヨト

# **Feedback mappings**

The third port reflection coefficient,  $\Gamma_3$ , is related to the normalised third port terminating impedance,  $z_3$ , as follows:

$$\Gamma_3 = \frac{z_3 - 1}{z_3 + 1} \tag{27}$$

We can substitute (27) into equation (18) to obtain  $S'_{ii}$  in terms of  $z_3$  as follows:

$$S'_{ij} = s_{ij} + \frac{s_{i3}s_{3j}\left\{\frac{z_3 - 1}{z_3 + 1}\right\}}{1 - s_{33}\left\{\frac{z_3 - 1}{z_3 + 1}\right\}}$$

(28)

Rearranging (28) we get:

$$S'_{ij} = s_{ij} + \frac{s_{i3}s_{3j}(z_3 - 1)}{(z_3 + 1) - s_{33}(z_3 - 1)}$$

(29)

From which  $z_3$  can be expressed in terms of  $S'_{ii}$  as follows:

$$z_{3} = \frac{s_{i3}s_{3j} + (S'_{ij} - s_{ij})(s_{33} + 1)}{s_{i3}s_{3j} + (S'_{ij} - s_{ij})(s_{33} - 1)}$$

(30)

# Feedback mappings

We can rearrange (30) into the form of yet another bilinear transformation as follows:

$$z_3 = \frac{A_{ij}S'_{ij} + C_{ij}}{B_{ij}S'_{ij} + D_{ij}}$$

(31)

Where  $A_{ij}$ ,  $B_{ij}$ ,  $C_{ij}$  and  $D_{ij}$  are feedback mapping coefficients defined as:

$$\begin{array}{l} A_{ij} = (s_{33} + 1) \\ B_{ij} = (s_{33} - 1) \\ C_{ij} = s_{i3}s_{3j} - s_{ij} (s_{33} + 1) \\ D_{ij} = s_{i3}s_{3j} - s_{ij} (s_{33} - 1) \end{array} \right\}$$

(32)

< ∃⇒

# **Feedback mappings**

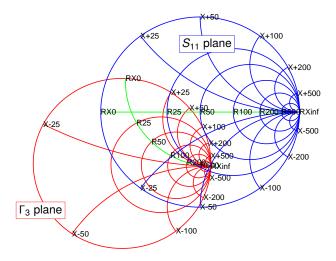

By separating equation (31) into real and imaginary parts we get expressions for the centres and radii of constant normalised third port resistance and reactance circles in the  $S'_{ii}$  plane. The centres are as follows:

$$\Gamma_{rij} = \left[ \frac{B_{ij}^{*}(C_{ij} - 2rD_{ij}) + D_{ij}A_{ij}^{*}}{2\left(|B_{ij}|^{2}r - Re(A_{ij}B_{ij}^{*})\right)} \right]$$

(33)

$$T_{xij} = -\left[ \frac{2(B_{ij}^{*}D_{ij})x - j(D_{ij}A_{ij}^{*} - C_{ij}B_{ij}^{*})}{2\left(|B_{ij}|^{2}x - Im(A_{ij}B_{ij}^{*})\right)} \right]$$

(34)

The radii are given by :-

Γ

$$\gamma_{rij} = \sqrt{|\Gamma_{rij}|^2 - \frac{|D_{ij}|^2 r - Re(D_{ij}^*C_{ij})}{|B_{ij}|^2 r - Re(A_{ij}B_{ij}^*)}}$$

(35)

$$\gamma_{xij} = \sqrt{|\Gamma_{xij}|^2 - \frac{|D_{ij}|^2 x - Im(D_{ij}^* C_{ij})}{|B_{ij}|^2 x - Im(A_{ij} B_{ij}^*)}}$$

(36)

Where : i = 1, 2 and j = 1, 2

# **Feedback mapping example :** S<sub>11</sub> **plane**

3

イロト イ理ト イヨト イヨト

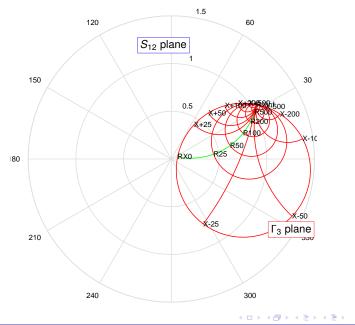

## Feedback mapping example : S<sub>12</sub> plane

э

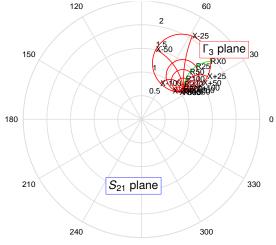

# Feedback mapping example : S<sub>21</sub> plane

770

э

▲ 돋 ▶ ▲ 돋 ▶ ...

# Feedback mapping example : S<sub>22</sub> plane

イロト イロト イヨト イヨト 一日

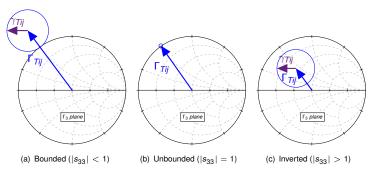

# **Classification of feedback mappings**

- Feedback mappings can be classified into three classes depending on the radius of the  $|\Gamma_3| = 1$  circle when mapped onto the respective *S*-plane[6].

- The three classes shall be referred to as "bounded", "unbounded" and "inverted", for reasons which will become apparent.

- The type of mapping is significant because it determines the maximum magnitude of S<sub>ij</sub> obtainable with a passive Γ<sub>3</sub>.

- ► This is of particular significance in negative resistance oscillator design, where we normally apply feedback with the express intention of maximising |*S*<sub>11</sub>|[1].

- ► We can determine the shape of the mapped Smith Chart on the S<sub>ij</sub> plane solely by the magnitude of s<sub>33</sub>, as follows[6]:

| <i>s</i> <sub>33</sub>   > 1 | Mapping is Bounded                              |

|------------------------------|-------------------------------------------------|

|                              | $ \Gamma_3  = 1$ circle maps to a circle        |

|                              | Mapping is Unbounded                            |

| $ s_{33}  = 1$               | $ \Gamma_3  = 1$ circle maps to a straight line |

| <i>s</i> <sub>33</sub>   < 1 | Mapping is Inverted                             |

| 333  < 1                     | $ \Gamma_3  = 1$ circle maps to a circle        |

★ E ► ★ E ►

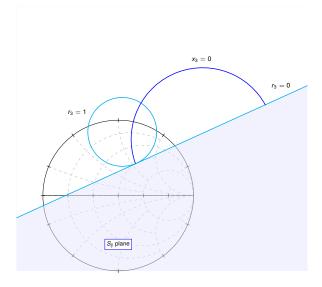

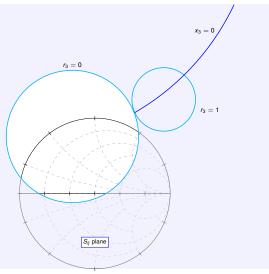

# **Bounded Mapping**

- If |s<sub>33</sub>| > 1 then the mapping is bounded

- The radius of the  $|\Gamma_3| = 1$  circle in the  $S'_{ij}$  plane is positive, as illustrated in figure 8

- Only finite values of S'<sub>ii</sub> can be achieved with a passive feedback termination. In practice, the optimum realisable feedback termination will be a lossless termination lying somewhere on the |Γ<sub>3</sub>| = 1 circle

Figure 8 : Bounded Feedback Mapping ( $|\Gamma_3|=1$  circle radius is positive

くロト (得) (ほ) (ほ)

# **Unbounded Mapping**

- If |s<sub>33</sub>| = 1 then the mapping is unbounded

- ► For an unbounded mapping the  $|\Gamma_3| = 1$ circle maps to a straight line in the  $S'_{ij}$ plane, therefore the radius of the mapped  $|\Gamma_3| = 1$  circle is infinite, as shown in figure 9

- An infinite value of S'<sub>ii</sub> can be achieved using a lossless third-port termination having the exact value :

$$\Gamma_3 = \frac{1}{s_{33}} \qquad (37)$$

$\begin{array}{l} \mbox{Figure 9}: \mbox{Unbounded Feedback Mapping } (|\Gamma_3| = 1 \mbox{ circle radius is infinite}) \\ & < \square \mathrel{\triangleright} < \square \mathrel{\triangleright} < \square \mathrel{\triangleright} < \square \mathrel{\triangleright} < \square \mathrel{\bullet} < \square \\ \end{array}$

Lecture 8 - Three-port S-Parameter design techniques

Slide36 of 46

# **Inverted Mapping**

- If |s<sub>33</sub>| < 1 then the mapping is inverted

- For an inverted mapping the radius of the  $|\Gamma_3| = 1$  circle in the  $S'_{ij}$  plane is negative, meaning that the mapped  $\Gamma_3$ Smith Chart is turned 'inside out' as shown in figure 10

- An infinite value of S'<sub>ii</sub> could, in theory, be obtained with a passive, lossy, feedback termination having the exact value :

$$\Gamma_3 = \frac{1}{s_{33}} \qquad (38)$$

Figure 10 : Inverted Feedback Mapping ( $|\Gamma_3|=1$  circle radius is negative)

Slide37 of 46

< ⊒ >

## **Table of Contents**

Three-port immittance parameters

Three-port S-parameters

Configuration conversion

Feedback mappings

Application of three-port design techniques

Reverse feedback mappings

イロト イポト イヨト イヨト

# Generating negative resistance in transistors

- One approach to negative resistance transistor oscillator design is to treat the transistor as a two-port network, induce negative resistance at one port and couple the output power from the other port. Let us therefore assume that we need to design a single transistor two-port sub-circuit having  $|S_{ij}| > 1$ .

- Figure ?? shows series feedback two-port sub-circuits created by adding a passive series feedback termination, Γ<sub>3</sub>, to the common port of a transistor in the three possible configurations, with Port 2 of the sub-circuit terminated in the system characteristic impedance, Z<sub>o</sub>.

- Bias circuitry has been omitted for simplicity. To implement an oscillator using the sub-circuits in figure ??, we need to couple a passive resonator to Port 1.

# Generating negative resistance in transistors

The following equation gives the optimum lossless series feedback termination for negative resistance generation, in terms of the original device two-port *S*-parameters:

$$\Gamma_{3opt} = 1 \angle \arctan\left(\frac{-4lm(\xi)}{4Re(\xi) - |\xi|^2}\right)$$

(39)

Since  $\Phi_{3opt}$ , the phase angle of the feedback reflection coefficient,  $\Gamma_{3opt}$ , determines whether the feedback reactance is capacitive or inductive, the implications of equation (39) can be summarised as follows:

| $Im(\xi) > 0$ | Optimum feedback termination is capacitive |

|---------------|--------------------------------------------|

| $lm(\xi) = 0$ | Optimum feedback termination is resistive  |

| $Im(\xi) < 0$ | Optimum feedback termination is inductive  |

Thus a 'rule of thumb' can be stated as follows :

'the type of series feedback reactance required to generate negative resistance in a given transistor configuration depends only on the sign of the imaginary part of the sum of the device two-port S-parameters for that configuration'[7].

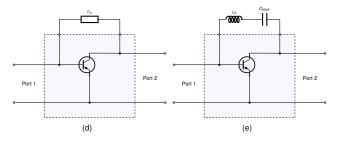

#### The active isolator

We can apply feedback mappings to help us design an *active isolator* based on a single transistor, the goal being to apply feedback so as to minimise  $S_{12}$ . The feedback can be either shunt or series type. The value of feedback termination,  $\Gamma_3$ , required to achieve unilateralisation can be determined by setting  $S_{12} = 0$  in equation (18) and solving for  $\Gamma_3$ :

$$\Gamma_3 = \frac{s_{12}}{s_{12}s_{33} - s_{13}s_{32}} \tag{40}$$

If the required value of implies an inductive shunt feedback termination, we need to include a DC blocking capacitor,  $C_{block}$ , to separate the collector and base DC bias voltages, as shown in figure 11(e). This capacitor must be large enough so that its reactance will be negligible at the frequency of operation.

Figure 11 : Unilateralisation of a transistor using shunt feedback

## **Table of Contents**

Three-port immittance parameters

Three-port S-parameters

Configuration conversion

Feedback mappings

Application of three-port design techniques

Reverse feedback mappings

(4 個) トイヨト イヨト

### **Reverse feedback mappings**

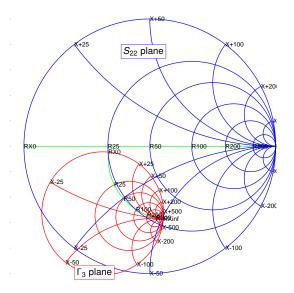

An alternative approach to analysing the effect of feedback on a transistor is to plot circles of constant  $|S_{ij}|$  on the  $\Gamma_3$  plane.

We refer to these as *reverse mapping* although they are not mappings of the entire  $S_{ij}$ , and only provide magnitude information, not phase information about the *S*-parameters obtainable. They are, nonetheless, a useful tool in certain circumstances.

Consider a reduced two-port consisting of a transistor with a shunt or series feedback termination,  $\Gamma_3$ , as shown in figure 4(b) or 4(e). We have already established that any point on the  $S_{ij}$  plane corresponds to a point on the  $\Gamma_3$  plane and vice versa according to the bilinear transformation of (18).

From equation (18), we can state the magnitude of the reduced two-port *S*-parameter as follows:

$$|S'_{ij}| = \left|rac{s_{ij} - (s_{ij}s_{33} - s_{i3}s_{3j})\Gamma_3}{1 - s_{33}\Gamma_3}

ight|$$

Which can be rewritten as:

$$|S'_{ij}| = \left|\frac{s_{ij} - \Delta_{ij}\Gamma_3}{1 - s_{33}\Gamma_3}\right|$$

(41)

ヘロト ヘ戸ト ヘヨト ヘヨト

Where :  $\Delta_{ij} = s_{ij}s_{33} - s_{i3}s_{3j}$

#### **Reverse feedback mappings**

Equation (41) can be rearranged into an equation that describes a circle in the reduced two-port  $S_{ij}$  plane with a centre at:

$$\Gamma_{Tij} = \frac{|S'_{ij}|^2 s^*_{33} - s_{ij} \Delta^*_{ij}}{|S'_{ij}|^2 |s_{33}|^2 - |\Delta_{ij}|^2}$$

(42)

and a radius given by:

$$\gamma_{Tij} = \sqrt{\left[|\Gamma_{Tij}|^2 - \frac{|S'_{ij}|^2 - |s_{ij}|^2}{|S'_{ij}|^2 |s_{33}|^2 - |\Delta_{ij}|^2}\right]}$$

(43)

Further manipulation of equation (43) results in the following, simpler expression:

$$\gamma_{Tij} = \frac{|S'_{ij}||\Delta^*_{ij} - s^*_{33}s_{ij}|}{|S'_{ij}|^2|s_{33}|^2 - |\Delta_{ij}|^2}$$

(44)

- ► If the required value of  $|S_{ij}|$  is known then the constant  $|S_{ij}|$  circle allows the corresponding values of  $\Gamma_3$  to be determined.

- Since every point on a constant |S<sub>ij</sub>| circle on the Γ<sub>3</sub> plane represents a complex value of Γ<sub>3</sub>, there are an infinite number of different values of Γ<sub>3</sub> for any given value of |S<sub>ij</sub>|

イロト イ押ト イヨト イヨトー

## **Reverse feedback mappings**

Consider the specific case of the  $|S_{ij}| = 1$  circle, which, in the case of  $S_{11}$  and  $S_{22}$ , defines the boundary between positive and negative resistance at the input and output ports of the device, respectively.

Figure 12 : Reverse feedback mappings

# References

#### G R Basawapatna and R B Stancliff.

A unified approach to the design of wideband microwave solid state oscillators.

IEEE Transactions on Microwave Theory and Techniques, MTT-27(5):379–385, May 1979.

#### G Bodway.

Circuit Design and Characterisation of transistors by means of three-port scattering parameters.

Microwave Journal, 11(5):4-27, May 1968.

Ralph S Carson.

High Frequency Amplifiers. John Wiley and Sons, New York, 1975.

D Eungdamrong and D K Misra.

Working with Transistor S-Parameters. *RF Design*, pages 38–42, January 2002.

A Khanna.

Three-port S-parameters ease GaAs MESFET Designing. *Microwaves and RF*, pages 81–84, November 1985.

C Poole.

MESFET Oscillator design based on feedback mapping classification.

In 33rd Midwest Symposium on Circuits and Systems, volume 1, pages 609–612, Calgary, Canada, August 1990. 33rd Midwest Symposium on Circuits and Systems.

C. Poole and I. Z. Darwazeh.

A Simplified Approach to Predicting Negative Resistance in a Microwave Transistor with Series Feedback

Slide46 of 46